# Cutting Cost and Resolution Enabled by Novel Photonic Technologies for Next–Generation Probe Cards Manufacturing

Dr. Ksenija Varga, Dr. Thomas Uhrmann Business Development Management EV Group

4th Annual SWTest Asia | Hsinchu, Taiwan, November 2-3, 2023

EV Group: Company Overview, Novel Photonic Technologies.

Maskless Exposure Technology: Motivation for Evaluation: Objectives & Goals.

Methods, Materials, Procedures.

Key Data & Discussion.

$(\rightarrow)$

Newest EVG's Technology: NanoCleave<sup>™</sup>.

Summary & Conclusions.

### EV Group | Company Overview

#### **EV Group | Novel Photonic Technologies**

Leading supplier of wafer processing equipment for the MEMS, nanotechnology & semiconductors markets.

Founded in 1980 by DI Erich and Aya Maria Thallner. More than 1300 employees worldwide.

Headquarters in Austria, with fully owned subsidiaries in the USA, Japan, South Korea, China, Taiwan & Malaysia.

Maskless Exposure Technology<sup>™</sup> | Motivation for Evaluation: Objectives & Goals E V G

#### > INTRODUCTION / BACKGROUND

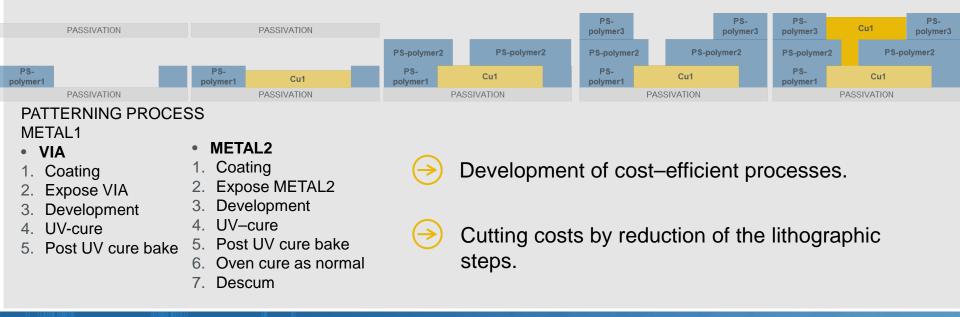

- Fine pitch probe cards interconnect formation: several lithographic patterning steps.

- Process is connected to high CoO.

#### EV Group Proprietary and Classified

#### **MLE<sup>™</sup> | Methods, Materials, Procedures**

#

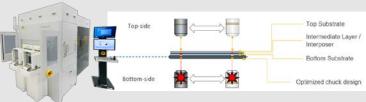

- VIS top—side alignment & backside alignment.

- Advanced Distortion Function: crucial for advanced packaging.

- High autofocus ±50 µm, high dept of focus ±12 µm.

- Die annotation feature.

| PARAMETER              | SPECIFICATION                                           |

|------------------------|---------------------------------------------------------|

| Exposure Source        | HP UV – Laser Diode (LD)                                |

| Exposure Spectrum [nm] | 375, 405 and every mix                                  |

| CD L/S [µm]            | < 2                                                     |

| Substrate Sizes [inch] | 6" – 12"                                                |

| Wafer Layout [format]  | GDS II (standard)<br>Gerber, OASIS, ODB++<br>(optional) |

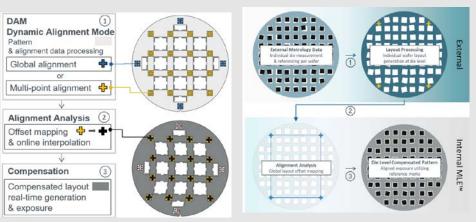

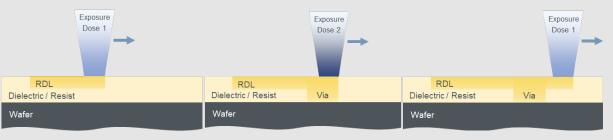

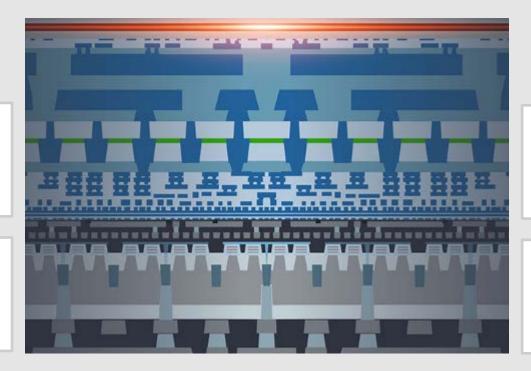

Die-level compensation schematic process flow

#### **MLE<sup>™</sup> | Methods, Materials, Procedures**

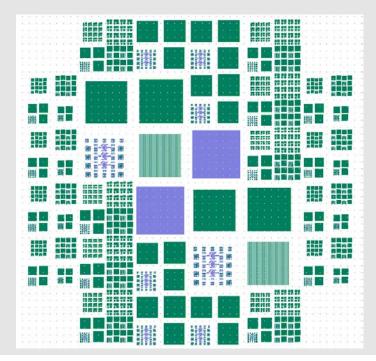

### TEST LAYOUT

Containing various test fields scaled up/down to different sizes written on 1 wafer.

#### EFFICIENT PROCESS EVALUATION & OPTIMIZATION!

#### **MLE<sup>™</sup> | Methods, Materials, Procedures**

#### EXPERIMENTAL SETUP

- Evaluated dose range: 10–450 mJ/cm<sup>2</sup>.

- TOK resist, positive tone.

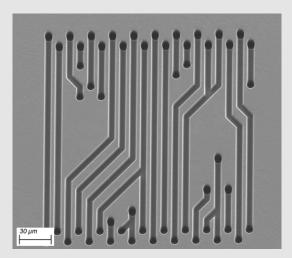

Design layout with dense RDL and VIAs connections

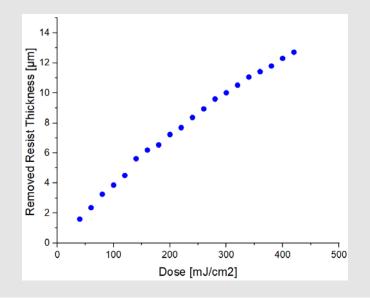

#### CONTRST CURVE

- To optimize the multi-level exposure an understanding of dose dependency on the penetration depth is required.

- Matrix where dose/wavelength/focus can be adjusted via recipe.

Minimum exposure dose required to initiate reaction.

Linear behavior at higher exposure dose

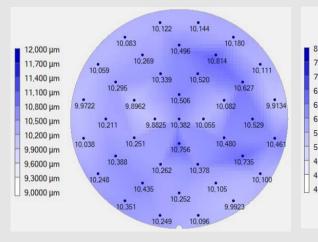

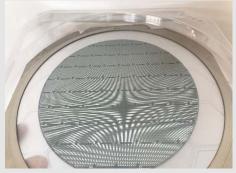

### SPECTRAL REFLECTANCE IMAGES

Estimation of the FT nonuniformity.

5.5223 5.3329 8,0000 µm 5.8707  $\diamond$ 5,2758 5,3935 7,6000 µm 5.3479 5.3095 5,2750 7,2000 µm 5 8423 5,2556 5,6210 6.8000 µm 5,3288 5,3700 4.8121 5.4197 5 1467 6,4000 µm 6.0000 µm 5 3134 5 8710 5 6953 5 3788 5 7822 5.6000 µm 5.5100 5.7631 5,6235 5.0580 5.3675 5.2000 um 5.6490 5,7134 4,8000 µm 5 4478 5 3628 5 2880 4.4000 um 5 0710 5,7124 5.5062 4.0000 um 5.3033 5,1196 4 8732 5.3082 5,0890

5,4362

5,4606

Resist surfaces generated via multi–level exposure is not significantly deviating from the original spin–coated surface.

Nonuniformity measurement after spin–coating process.

Nonuniformity measurement after exposure with a defined penetration depth & resist development.

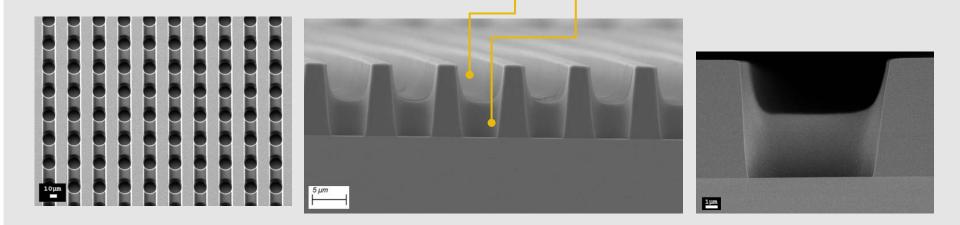

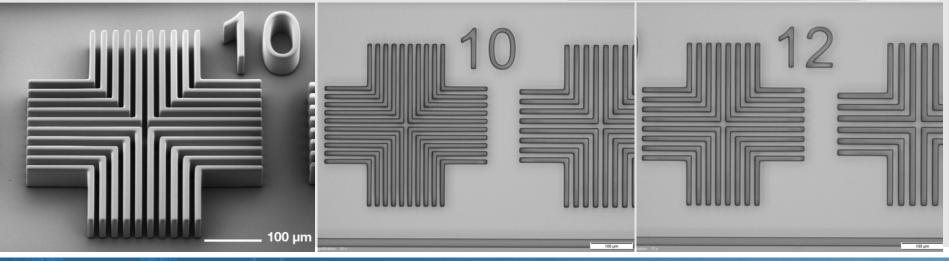

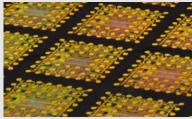

#### SEM IMAGES of DUAL-LAYERS

High dept–of–focus allows good control of sidewall profile and resolution throughout the resist layer thickness.

RDL VIA

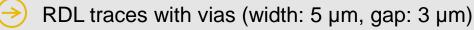

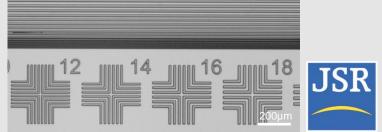

# SEM IMAGES

- Baseline evaluation of line–space variation patterning performance.

- Pos. TOK P–W1000T

- Layer thickness: 8 µm

- Aspect ratio 4:1, sidewall angle up to 87°

# **tok**

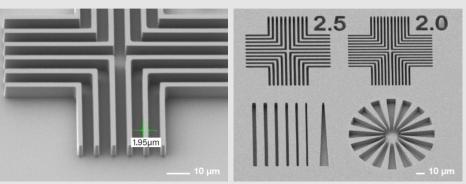

# SEM IMAGES

- Thick resist applications.

- JSR THB 151N, negative tone.

- Layer thickness: 50 µm, AR 5:1

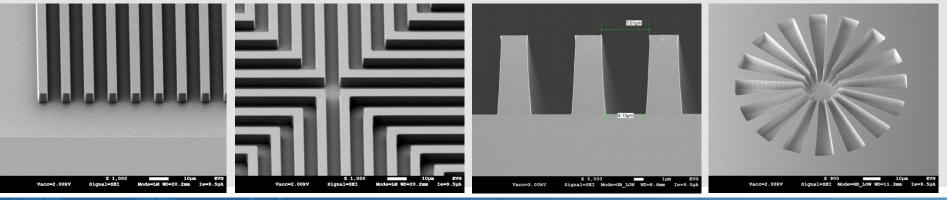

- SEM IMAGES

- NEW DEVELOPMENT: negative tone dielectrics for fine pitch probe cards RDL patterning.

- Layer Thickness: 7 8 μm (after soft bake), AR: > 2:1

#### MLE<sup>™</sup> | Follow–Up Work

#### DIE ANNOTATION FEATURE

- Data generation "on–the–fly" for each wafer individually.

- Available Annotation Types: DataMatrix, QR Code, Aztec, PDF417 etc.

- Important for traceability in semiconductor supply chain.

# ightarrow VARIABLES USED

- LotID, SubstrateID, SubstrateAquiredID, CellID

- EquipmentName, ModuleName, SerialNumber

- RecipeName, RecipeNamespace

- ProcessJobID, ControllJobID

#### **MLE<sup>™</sup> | Follow–Up Work**

Annotations are created as templates on LITHOSCALE<sup>®</sup> and can be used in various recipes.

| Add New Annotation                                                                     |                                                                                            | Add New Annotation |    |    |           |                                                                                                                                    |                                                                                   |                         |             |   |    |        |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------|----|----|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|-------------|---|----|--------|

|                                                                                        |                                                                                            |                    |    |    |           |                                                                                                                                    |                                                                                   | 11-10                   |             |   |    |        |

| Template Info<br>Name :                                                                | Cell_Code                                                                                  |                    |    |    |           | Template Info<br>Name :                                                                                                            | Cell_C                                                                            | ode                     |             | - |    |        |

| Annotation Description<br>Content:<br>Display Mode:<br>Code Type:<br>Width:<br>Height: |                                                                                            | μm<br>μm           | •  | ₫I |           |                                                                                                                                    |                                                                                   | 1D)<br>•<br>•<br>50d μm |             | ļ |    |        |

| ensure the code pixels                                                                 | oper width and height for the co<br>are large enough.<br>ation is just a preview and may n |                    | e. | 2  |           | Annotation Editing Info<br>"Consider setting a pre-<br>ensure the code pixels<br>"The displayed annota<br>contain the final data a | oper width and height for th<br>are large enough.<br>tion is just a preview and m | e code, to<br>ay not ye | e<br>t<br>v | ł |    |        |

|                                                                                        |                                                                                            |                    |    |    | QK Cancel |                                                                                                                                    |                                                                                   |                         |             |   | QK | Çancel |

DATA MATRIX

**QR CODE**

#### NanoCleave<sup>™</sup> | IR Laser Release

IR laser-initiated release of any ultrathin film or layer from silicon carriers with nanometer precision.

Revolutionizing 3D & heterogenous integration as well as material transfer.

Front–end compatible carrier technology for further integration of fusion and hybrid bonding processes.

Enabling silicon carrier wafers in advance packaging processes such as FoWLP & 3D SIC.

#### NanoCleave<sup>™</sup> | IR Laser Release

#### > INTRODUCTION

- Technology utilizes IR laser & inorganic release materials to enable laser debonding on Si.

- This eliminates the need for glass substrates in advanced packaging.

- Temperature & glass carrier compatibility issues are avoided.

- Ability to transfer ultra-thin layers via carriers in front-end processing is enabled.

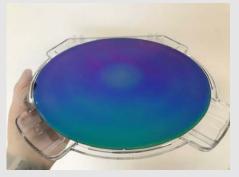

300 mm fusion bonded wafers release

300 mm molded wafer release

200 mm temporary bonded thin device wafer release

#### NanoCleave<sup>™</sup> | IR Laser Release

#### **INTRODUCTION**

The nanometer-precision of new process supports advanced semiconductor device roadmaps calling for thinner device layers & packages.

#### APPLICATION in FO WLP

- Release for "RDL first".

- Temporary bonding for warpage control for "chip first" enables thinning & backside processing.

Source: Brewer Science

MASKLESS MANUFACTURING ACCOMPLISHES:

#### TECHNOLOGY SCALING for FINE PITCH PROBE CARDS

High resolution patterning achieving <2 µm L/S</li>

#### DESIGN FLEXIBILITY

- Layout independent from chip size

- Multi–die architectures, die–level patterning

# MARKET LEADERSHIP

- Fast tape-out

- Adaptation to customer needs

#### EVG's Photonic Technologies | Summary & Conclusions

#### MASKLESS MANUFACTURING ACCOMPLISHES:

# ECONOMICAL BENEFITS

By dual-layer exposure of resists by cutting the lithographic steps.

#### SUSTAINABLE INDUSTRY

Short supply chain contributes to low ecological footprint

#### Recently launched IR Laser Release Technology

Enables cutting the costs through thin layer transfer & elimination of needed glass substrates.

### Thank you for your attention!

K.Varga@EVGroup.com

#### Wafer is coated with black resist and world map is patterned on LITHOSCALE®

Data design and specifications may not simultaneously apply, or depend on individual addresses ar equipment names that contain the letters or words 'EVG' or 'EV Group or EZRIN EZ Redease®, CEMINI®, HERCULES®, HyperIntegration®, IQ Aligner®, Low readout the second statement of Brewer Science, Inc. Other product and compare ZoneBOND® is a registered trademark of Brewer Science, Inc. Other product and compare the second statement of Brewer Science, Inc. Other product and compare and second statement of Brewer Science, Inc. Other product and compare the second statement of Brewer Science, Inc. Other product and compare the second statement of process conditions and materials and may vary accordingly. EVG (as well as the following names and acronyms are registered that NanoSpray ", NIL-COM®, NILPhotonics®, OmniSpray®, commarks of their respective owners.

-

C

ly, EVC reserve the definition of the definition and an exclusion with an proceeding all realisments logoes, website tered tradematic and/or the property of EV Group. Combands. CoverSpr 114, E285, E2 Bondo, E2O6, E2 Debondo, Sprayo, Smill Edges, characterize, standardset, the Tople of Company, traverstrong to the process to the process